# Design of Ultra-Low Power Biopotential Amplifiers for Biosignal Acquisition Applications

Fan Zhang, Student Member, IEEE, Jeremy Holleman, Member, IEEE, and Brian P. Otis, Senior Member, IEEE

Abstract—Rapid development in miniature implantable electronics are expediting advances in neuroscience by allowing observation and control of neural activities. The first stage of an implantable biosignal recording system, a low-noise biopotential amplifier (BPA), is critical to the overall power and noise performance of the system. In order to integrate a large number of front-end amplifiers in multichannel implantable systems, the power consumption of each amplifier must be minimized. This paper introduces a closed-loop complementary-input amplifier, which has a bandwidth of 0.05 Hz to 10.5 kHz, an input-referred noise of 2.2  $\mu V_{rms}$ , and a power dissipation of 12  $\mu W$ . As a point of comparison, a standard telescopic-cascode closed-loop amplifier with a 0.4 Hz to 8.5 kHz bandwidth, input-referred noise of 3.2  $\mu V_{rms}$ , and power dissipation of 12.5  $\mu W$  is presented. Also for comparison, we show results from an open-loop complementary-input amplifier that exhibits an input-referred noise of 3.6  $\mu V_{rms}$  while consuming 800 nW of power. The two closed-loop amplifiers are fabricated in a 0.13  $\mu$ m CMOS process. The open-loop amplifier is fabricated in a 0.5  $\mu$ m SOI-BiCMOS process. All three amplifiers operate with a 1 V supply.

Index Terms—Analog integrated circuits, biosignal amplifier, biopotential amplifier, low noise, low-power circuit design, neural amplifier, noise efficiency factor.

#### I. INTRODUCTION

R APID advances in ultra-low power microelectronic design have given rise to a new paradigm in neuroscience and clinical research for treating brain disorders. Electrical engineers and neuroscientists have made dramatic progress in designing neural-electronic interfaces to operate as miniature, lightweight, chronically implanted wireless systems. Implantable systems for chronic use require ultra-low power operation to minimize heat dissipation, avoid frequent battery replacement, and enable operation from wirelessly-delivered or harvested energy (e.g., thermoelectric generation).

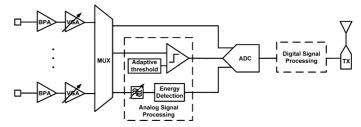

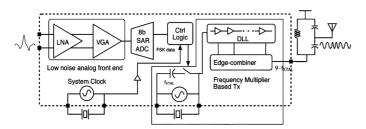

An example of a biopotential recording system is illustrated in Fig. 1. The acquisition of microvolt-level neural signals requires amplification and signal conditioning. The amplified sig-

Manuscript received March 24, 2011; revised July 04, 2011 and September 14, 2011; accepted November 09, 2011. Date of publication January 11, 2012; date of current version July 24, 2012. This paper was recommended by Associate Editor C. Van Hoof.

F. Zhang and B. P. Otis are with the Department of Electrical Engineering, University of Washington, Seattle, WA 98195 USA (e-mail: fz2@u.washington.edu; botis@uw.edu).

J. Holleman is with the Department of Electrical Engineering and Computer Science, University of Tennessee, Knoxville, TN 37917 USA (e-mail: jeremy. holleman@utk.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TBCAS.2011.2177089

Fig. 1. A generic block diagram for a biopotential-recording system.

nals may be processed to extract the most salient information and reduce the data rate. The signal is then transmitted to an external device, where the information is used to diagnose neural disorders or infer neural state, for example. Monolithic amplifiers have been used for electrophysiological recording signals for decades [1]–[3]. The large time constants inherent in the amplifier dynamics typically preclude timesharing of a single amplifier between multiple electrodes [4]. Therefore, multichannel systems typically use one amplifier per channel, imposing severe power constraints on the amplifier design.

Table I shows a few examples of the electrical characteristics of some electrophysiological signals that are commonly of interest in neuroscience. Single-unit recordings provide the finest spatial resolution of the brain, but they typically incur relatively high power consumption due to the wide amplifier bandwidth required and high resulting datarate [5]. EEG, on the other hand, is non-invasive and has modest amplifier bandwidth constraints at the cost of low spatial resolution. ECoG is an invasive modality that uses non-penetrating electrodes and offers a compromise that is receiving increased attention in the neuroscience community. Though this paper focuses on BPAs for single unit recording, the concepts presented here can be adapted to systems requiring different bandwidths and noise performance.

Here we outline the basic design requirements of a spikebased recording amplifier. Typical extracellular action potentials, or spikes, have amplitudes up to 500  $\mu$ V, with much of the signal energy in the 100 Hz-7 kHz band. Low-frequency local field potentials (LFPs) have amplitudes as high as 5 mV and may contain signal energy below 1 Hz [6], [7]. The low amplitudes of the spikes require BPA gain of around 100 × up to a few kHz. Large DC-offsets at the electrode-tissue interface require offset cancellation or AC coupling. The input impedance of the amplifiers should be high enough (a few M $\Omega$ s at 1 kHz) to limit signal attenuation from the electrode-tissue interface. The input-referred noise of the BPAs should be kept below the background noise of the recording site ( $<10 \mu V$ ). The power dissipation should be kept as low as possible ( $\ll 100 \mu \text{W/channel}$ ) in a multichannel system to contain the heating of the tissue within a few degrees Celsius [8], [9]. Sufficient common-mode

|                              | Bandwidth  | Amplitude       | Spatial Resolution | Invasiveness        |

|------------------------------|------------|-----------------|--------------------|---------------------|

| Single-Unit                  | 0.1-7 kHz  | $< 500 \mu V$   | 0.2 mm             | invasive            |

| LFP (local field potential)  | < 200 Hz   | < 5 mV          | 1 mm               | moderately invasive |

| ECoG (electrocorticography)  | 0.5-200 Hz | $< 100 \ \mu V$ | 0.5 cm             | moderately invasive |

| EEG (electroencephalography) | < 100 Hz   | 10-20 μV        | 3 cm               | non-invasive        |

TABLE I

CHARACTERISTICS OF ELECTROPHYSIOLOGICAL SIGNALS

and power-supply rejection should also be ensured to reject the inevitable interference and supply noise. Lastly, the amplifiers should occupy small silicon areas to allow multiple instantiations in a larger system.

These requirements form the initial condition for our proposed design evolution. The paper is organized as follows: Section II gives an overview of the present state of the art. Section III presents an evolution of BPA designs that exhibit low noise while consuming minimal power, including a closed-loop telescopic differential BPA, an open-loop complementary-input single-ended BPA, and a closed-loop complementary-input differential BPA design. Section IV compares and contrasts the measurement results of the three amplifier designs. Section V presents an example system-level implementation using BPA3. Section VI presents the *in-vivo* measurement results recorded from a rat motor cortex and a mouse visual cortex. Section VII provides a detailed analysis on issues involved in using the proposed amplifiers in a multichannel system.

#### II. STATE-OF-THE-ART BIOPOTENTIAL AMPLIFIERS

The pioneering power-efficient neural recording ICs [1], [3], [8], [10], [11] typically consumed about 100  $\mu$ W to achieve <5  $\mu$ V<sub>rms</sub> of noise for 5–10 kHz bandwidth. Recently published amplifiers [12]–[14] have featured reduced power consumption in an effort to enable large recording arrays. Below we present a brief review of some representative techniques used in state-of-the-art low-power biopotential amplifier designs. More comprehensive reviews can be found in [4], [9], [15].

The oft-cited [8] presents many useful techniques for designing biopotential-recording amplifiers, including the use of capacitive feedback and pseudoresistors around an operational transconductance amplifier (OTA).

By reducing the number of current branches, the one-stage self-biased preamplifier in [14] achieves 4.9  $\mu V_{\rm rms}$  input-referred noise while drawing only 2  $\mu A$  under  $\pm 1.65~V$  supply.

The fully-differential folded-cascode preamplifier in [16] includes multiple adjustable parameters for various biopotential recording applications. While achieving 3.6  $\mu V_{\rm rms}$  input-referred noise over 20 Hz to 10 kHz, the current consumption is 8  $\mu A$  at  $\pm 1.7$  V supply. The extra current branches in the folded-cascode topology result in sub-optimal power-noise tradeoff.

The design in [12] employs a modified folded-cascode topology with severely scaled currents in the input and folded branches and source degeneration to reduce the power and noise contribution from the folded branches. However, the 4.5 M $\Omega$  degeneration resistors increase the area and voltage head-room required of the amplifier, requiring a 2.8 V supply voltage.

Other recent advances in the field include mixed-signal front-end for filtering and digitization [17]–[19]. With the trend

towards integrating analog and digital subsystems on a single die, it has become increasingly important for analog circuitry to operate from the 1 V supply typical of modern digital CMOS. This paper presents a power-efficient amplifier topology with a 1 V supply.

#### III. DESIGN OF LOW-NOISE BIOPOTENTIAL AMPLIFIERS

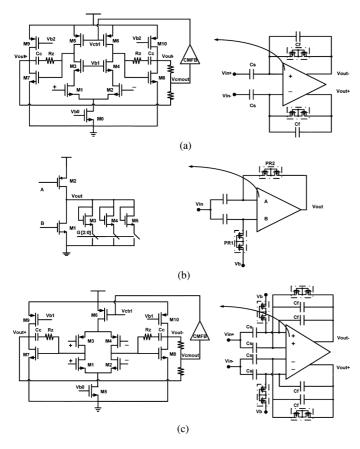

In this section, we show a logical progression of biopotential amplifiers by comparing and contrasting their design strategies. First, a closed-loop fully-differential telescopic amplifier (BPA1) is included as a "baseline" design to compare against the other designs. Then, an open-loop single-ended complementary-input amplifier (BPA2) serves as an instructional example to demonstrate a design technique with the potential to surpass the theoretical limit of the power-noise tradeoff of a conventional amplifier at the expense of PSRR. Lastly, combining the salient features of BPA1 and BPA2, we designed a closed-loop fully-differential complementary-input amplifier (BPA3) with excellent power-noise performance, sufficient linearity and power-supply rejection performances.

# A. Design of a Closed-Loop Fully-Differential Telescopic-Cascode Amplifier

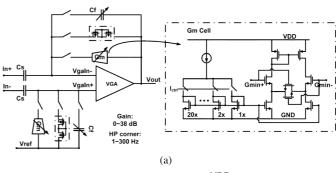

The schematic of a typical closed-loop telescopic BPA is shown in Fig. 2(a). The input signals are AC-coupled into the amplifier to reject large DC offsets from the electrode-tissue interface.  $C_s$  must be made small enough to avoid attenuation of the input signal from the electrode, but large enough to avoid attenuation from the capacitive divider it forms with the OTA input capacitance, which will increase input-referred noise, as shown in (1). Let  $\overline{v_{ni,\text{OTA}}^2}$  and  $\overline{v_{ni}^2}$  represent the input-referred noise of the OTA and the BPA, respectively.

$$\overline{v_{ni}^2} = \left(\frac{C_s + C_f + C_{\text{in}}}{C_s}\right)^2 \overline{v_{ni,\text{OTA}}^2} \tag{1}$$

The ratio  $C_s/C_f$  sets the mid-band gain of the amplifier to roughly 40 dB. We chose 180 fF for  $C_f$  to ensure sufficient mid-band gain while limiting the increase in the input-referred noise due to the input capacitive divider (1) to 12%. Pseudoresistors are used here as an area-efficient approach to bias the input transistors and form a sub-Hz high-pass frequency corner with  $C_f$  to accommodate EEG/LFP signals. Thick-oxide MOS transistors are used at the input to reduce gate leakage current, which could result in significant DC-offsets. The input-referred noise from the feedback pseudoresistors is

$$\overline{v_{ni,R}^2} = \left(\frac{V_{n,R}}{1 + j\omega R C_f}\right) \left(\frac{1}{A_{\text{CL}}^2}\right). \tag{2}$$

Let  $A_{\rm CL}$  represent the closed-loop gain of the BPA. Scaled by  $A_{\rm CL}^2$  and attenuated at 20 dB/dec after the sub-Hz frequency

|       | W/L (μm) | $I_d (\mu A)$ | Inv. Coeff | $g_m/I_d (V^{-1})$ | $ V_{GS}  -  V_t  $ (mV) |

|-------|----------|---------------|------------|--------------------|--------------------------|

| M1,2  | 616/2    | 3             | 0.023      | 27.56              | -154                     |

| M3,4  | 12/5     | 3             | 0.27       | 22                 | 102                      |

| M5,6  | 12.2/13  | 3             | 11.3       | 6.9                | 258                      |

| M0    | 109.8/8  | 6             | 0.54       | 19.4               | 7                        |

| M7,8  | 12/4     | 2.2           | 0.96       | 16.82              | 76                       |

| M9,10 | 8.6/3    | 2.2           | 1.92       | 13.64              | 103                      |

TABLE II

DEVICE PARAMETERS OF TELESCOPIC-CASCODE CLOSED-LOOP BIOPOTENTIAL AMPLIFIER

Fig. 2. Schematics of three low-noise biopotential amplifier designs. (a) Tele-scopic-cascode closed-loop amplifier (BPA1), (b) Complementary-input open-loop amplifier (BPA2), (c) Complementary-input closed-loop amplifier (BPA3).

corner  $(1)/(2\pi RC_f)$ , the noise contribution from the pseudoresistors at frequencies of interest is negligible compared to flicker or thermal noise. More detailed analysis on the noise contributed by pseudoresistors can be found in [4].

In order to lower the power consumption and ease integration with complex digital subsystems, the amplifier operates from a supply as low as 1 V. A two-stage fully-differential design was chosen to provide sufficient gain, signal swing, and supply rejection while operating from a 1 V supply. We simulated an open-loop gain of 69 dB. In addition, the fully-differential topology provides higher CMRR and PSRR when compared to its single-ended counterpart, critical for low-voltage supply conditions.

The input stage employs a telescopic cascode rather than a folded cascode because of its reduced number of active branches and because the small input amplitude precludes the need for a wide input swing in the first stage. We used NMOS input transistors because their higher  $g_m/I_D$  compared to PMOS transistors results in lower thermal noise, which dominates over flicker noise in this design.

To reduce noise, the transistors are carefully sized for appropriate inversion coefficient (IC) [20] as shown in Table II.

The input-referred thermal noise can be approximated as

$$v_{ni,th}^2 = \left(\frac{16kT}{3g_{m1}}\left(1 + \frac{g_{m5}}{g_{m1}}\right)\right)\Delta f. \tag{3}$$

The input-referred 1/f noise can be calculated as

$$v_{ni,1/f}^2 = \frac{1}{C_{ox}\Delta f} \cdot \left(\frac{K_n}{(WL)_1} + \frac{K_p g_{m5}^2}{(WL)_5 g_{m1}^2}\right). \tag{4}$$

Here,  $C_{ox}$  represents the gate dielectric capacitance while  $K_n$  and  $K_p$  denote the nFET and pFET flicker noise constants. The values are process-dependent and are on the order of  $10^{-13}$  V<sup>2</sup>-pF [21] with  $K_n > K_p$ . All the transistors, particularly the input pair, use large gate areas to reduce the 1/f noise. Similar to the  $v_{ni,th}$ , a low  $g_{m5}/g_{m1}$  ratio also reduces  $v_{ni,1/f}$ .

## B. Design of an Open-Loop Complementary-Input Amplifier

Although BPA1 achieves good power-noise performance, extra current was consumed in the differential input branches and the second stage. For a given bias current, open-loop amplifiers achieve superior noise performance at the expense of linearity, imprecise gain control and reduced power-supply rejection. In this section, we will present the design of an open-loop complementary-input single-ended BPA [22] that achieves an excellent power-noise tradeoff at the expense of PSRR.

Our open-loop design serves as an instructional extreme case that minimizes noise and power consumption. This design philosophy is motivated by the characteristics of the signals targeted by this amplifier. The small amplitude ( $\sim\!100~\mu\mathrm{V})$  of neural signals relaxes the linearity requirement compared to more general-purpose amplifiers. Gain precision is also not critical; the absolute signal amplitude is not as important as preservation of relative amplitudes. In addition, a stable power supply is also possible with careful system design and deployment.

Leveraging these design tradeoffs, we introduce the schematic shown in Fig. 2(b). The input signals are AC-coupled into the amplifier and the gates of the input transistors are biased using pseudoresistors. Diode-connected transistors  $M_{3-5}$  provide a means to vary the output conductance and thereby the gain and bandwidth.

|       | W/L (μm) | $I_d (\mu A)$ | Inv. Coeff | $g_m/I_d (V^{-1})$ | $ V_{GS}  -  V_t  $ (mV) |

|-------|----------|---------------|------------|--------------------|--------------------------|

| M1,2  | 552/2    | 3             | 0.022      | 27.53              | -152                     |

| M3,4  | 552/2    | 3             | 0.12       | 24.23              | -106                     |

| M5    | 110.4/8  | 6             | 0.54       | 19.4               | 5                        |

| M6    | 73.2/8   | 6             | 1.98       | 13.5               | 103                      |

| M7,8  | 12/4     | 2.1           | 0.93       | 16.96              | 30                       |

| M9,10 | 8.6/3    | 2.1           | 1.93       | 13.62              | 103                      |

TABLE III

DEVICE PARAMETERS OF COMPLEMENTARY-INPUT CLOSED-LOOP BIOPOTENTIAL AMPLIFIERS

By driving the gates of both  $M_1$  and  $M_2$ , the total transconductance efficiency of the amplifier (which determines noise efficiency) is  $2g_m/I_d$ , theoretically allowing a noise efficiency factor (NEF) less than unity. Assuming the two transistors have equal transconductance, the amplifier's transconductance  $G_m$  is effectively doubled. The input-referred thermal noise can be expressed as

$$v_{ni,th}^2 = \left(\frac{8kT}{3 \cdot (g_{m1} + g_{m2})}\right) \Delta f. \tag{5}$$

If  $g_{m1} = g_{m2}$ , then

$$v_{ni,th}^2 = \left(\frac{8kT}{3q_{m1} \cdot 2}\right) \Delta f. \tag{6}$$

A common-source amplifier with current source load will have more thermal noise than the topology proposed here by a factor ranging from  $\sqrt{2}$  for a noiseless current source (i.e.,  $g_m=0$ ) to 2 for a current source with  $g_m$  equal to that of the amplifying transistor. The minimum practical  $g_m$  for the current source load is dictated by supply headroom and the required overdrive voltage.

Because the positive supply is connected to the source of  $M_2$ , supply noise is coupled to the output through  $M_2$ . The power-supply rejection ratio can be expected to be approximately  $(g_{m2})/(g_{m1}+g_{m2})$ , or about 6 dB if  $M_{1,2}$  have equal transconductance. Therefore, in order to realize the potential noise performance of BPA2, a stable supply with noise comparable to the amplifier's input-referred noise must be provided.

# C. Design of a Closed-Loop Fully-Differential Complementary-Input Amplifier

Leveraging BPA2's power-efficient complementary-input topology, we further improved the PSRR, linearity, and precision of gain/bandwidth control in a closed-loop fully-differential amplifier design (BPA3) [23]. The schematic of BPA3 is shown in Fig. 2(c). BPA3 has the same bias current and mid-band gain as BPA1. We also retain the two-stage fully-differential design with similar compensation and CMFB schemes.

Similar to BPA2, we drive both the NMOS and PMOS input pairs to allow a significant reduction in the input-referred noise. Two small-signal gain paths from the NMOS and PMOS inputs necessitate two capacitive feedback paths from the output to the gates of both input transistors. The open-loop gain is simulated to be >70 dB. The increase in the input-referred noise from the capacitive divider (1) at both the NMOS and PMOS inputs

are found to be approximately 10%. The complementary-input strategy doubles the amplifier's effective transconductance. As a result, the input-referred noise voltage is reduced by a factor of  $\sqrt{2}$ , similar to its open-loop counterpart. The input-referred thermal noise power is twice that of BPA2 because differential branches double the output noise. If  $g_{m1}=g_{m3}$ , it can be expressed as

$$v_{ni,th}^2 = \left(\frac{16kT}{3g_{m1} \cdot 2}\right) \Delta f. \tag{7}$$

Similarly, (3) shows the input-referred thermal noise for BPA1. If  $g_{m5} = 0$ , than (3) reduces to

$$v_{ni,th}^2 = \left(\frac{16kT}{3q_{m1}}\right)\Delta f. \tag{8}$$

A comparison between (7) and (8) reveals that the input-referred noise voltage of BPA3 is approximately  $1/\sqrt{2}$  that of BPA1. Table III shows the parameters and operating conditions of each transistor in the OTA. The input-referred flicker noise from the input devices can be approximated by

$$v_{ni,1/f}^{2} = \left(\frac{1}{C_{ox}\Delta f} \cdot \left(\frac{K_{n}g_{m1}^{2}}{(WL)_{1}} + \frac{K_{p}g_{m3}^{2}}{(WL)_{3}}\right) \cdot \frac{1}{(g_{m1} + g_{m3})^{2}}\right).$$

(9)

If  $g_{m1} = g_{m3}$ , then

$$v_{ni,1/f}^2 = \frac{1}{4C_{ox}\Delta f} \cdot \left(\frac{K_n}{(WL)_1} + \frac{K_p}{(WL)_3}\right).$$

(10)

We would also like to compare the 1/f noise of BPA1 with that of BPA3. In BPA1, if  $g_{m5} = 0$ , (4) reduces to

$$v_{ni,1/f}^2 = \frac{1}{C_{ox}\Delta f} \cdot \left(\frac{K_n}{(WL)_1}\right). \tag{11}$$

If we assume  $(K_n)/((WL)_1) = (K_p)/((WL)_3)$  in (9) for simplicity, then the net input-referred flicker noise voltage of BPA3 is  $1/\sqrt{2}$  that of BPA1. Notice that the complementary-input strategy has similar influence on the input-referred thermal and flicker noise.

Because the input also drives the PMOS transistor pair  $M_{3,4}$ , the transconductances of  $M_{3,4}$  not only contributes to the differential gain, but also the common-mode gain. To ensure high CMRR/PSRR, we use dual tail current sources in the first stage to degenerate the common-mode transconductance, thus reducing the common-mode gain.

Fig. 3. (a) Differential-mode gain path. (b) CMFB gain path.

The common-mode gain  $(A_{cm})$  and the gain of power-supply interference  $(A_{ps})$  can be expressed as

$$A_{\rm cm} = \frac{V_{\rm out}}{V_{\rm in,cm}} \simeq \frac{(g_{o5} + g_{o6})g_{m8}/(g_{o1}g_{o2})}{1 + sC_c/(g_{o5} + g_{o6})}.$$

(12)

Any variation in the supply is attenuated by approximately  $(g_{m6})/((g_{m3}+g_{m4}))\cdot(1-(V_{g6})/(V_{dd}))$  before being amplified by the  $g_m$  mismatches in  $M_{3,4}$  (14). Let  $g_{o1,2}$  denote the output conductance of the first and second stage,  $g_{o5,6}$  denote the output conductance of current source transistors  $M_{5,6}$ ,  $g_{m8}$  denotes the transconductance of the second stage,  $\Delta g_m$  denotes the  $g_m$  mismatch in  $M_{3,4}$ , and  $C_c$  denotes the compensation capacitor.

$$A_{\rm ps} = \frac{V_{\rm out}}{V_{\rm in, supply}} \simeq \frac{\Delta g_m \gamma g_{m8}/(g_{o1}g_{o2})}{1 + sC_c/\Delta g_m} \bigg|$$

$$\gamma = \frac{g_{m6}}{(g_{m3} + g_{m4})} \cdot \left(1 - \frac{V_{g6}}{V_{dd}}\right)$$

(13)

The design of the second stage is focused on ensuring sufficient output swing (differential peak-to-peak over 1 V) while achieving a reasonable gain (20 dB).

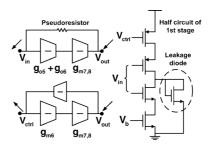

We employed continuous-time CMFB, with the output common-mode voltage sensed using two large resistors. The output of the CMFB amplifier controls the gate voltage of  $M_6$  to adjust the common-mode voltage of the first stage.

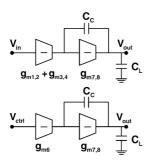

The signal propagation of the common-mode feedback path of BPA3 consists of two parts: from the average output  $V_{\rm cmout}$  to the feedback control  $V_{\rm ctrl}$ , and from  $V_{\rm ctrl}$  to the amplifier output. The first part of the CMFB path has a wide bandwidth and small DC gain ( $\simeq$ 1); the second part determines the CMFB frequency response as illustrated in Fig. 3. Let  $g_{m1-4,6-8}$  denote the transconductance of the corresponding transistors,  $C_c$  and  $C_L$  denote the compensation and load capacitors,  $g_{o1}$  and  $g_{o2}$  denote the total output conductances of stage 1 and 2. Then

$$A_{\text{cmfb}} = \frac{V_{\text{out,CM}}}{V_{\text{ctrl}}}$$

$$= \frac{-sg_{m6}C_c + g_{m6}g_{m7,8}}{s^2C_cC_L + sC_cg_{m7,8} + g_{o1}g_{o2}}$$

$$A_{\text{dm}} = \frac{V_{\text{out,DM}}}{V_{\text{in,dm}}}$$

$$= \frac{-s(g_{m1,2} + g_{m3,4})C_c + (g_{m1,2} + g_{m3,4})g_{m7,8}}{s^2C_cC_L + sC_cg_{m7,8} + g_{o1}g_{o2}}.$$

(14)

Fig. 4. Closed-loop amplifier start-up concern alleviated by adding a leakage path through a diode-connected transistor at the first-stage output.

Both the differential and common-mode gains share the compensation capacitor  $C_c$  and  $g_{m7.8}$  stage. The similarity of the transfer functions leads to a stable CMFB path if the differentialmode path is unity-gain stable. This CMFB topology achieves both high gain and bandwidth, while saving power by sharing one CMFB circuit between both the first and second stages. A brief analysis of the common mode circuit shows that the closed loop common-mode gain of the amplifier (including the effect of CMFB) is  $V_{\it oc}/V_{\it ic}=A_{\it cm}/(1+A_{\it cmfb})$  where  $A_{\it cm}$  is the amplifier's common-mode gain, and A<sub>cmfb</sub> is the combined gain of the common-mode detection circuit and the commonmode control (i.e.,  $A_{cmfb} = g_{m6}/(g_{o1} + g_{o3})$  if the gain of the block labeled "CMFB" in Fig. 2 is unity.) A high gain-bandwidth product in the CMFB loop reduces the common-mode voltage gain while leaving the differential-mode voltage gain unaffected. Thus, increasing the CMFB loop bandwidth will improve CMRR at higher frequencies.

In order to provide DC feedback and bias the input transistors, the outputs are fed back through pseudoresistors to bias the gates of the NMOS input transistors  $M_{1,2}$ . However, this feedback inevitably forms a positive feedback loop at low frequencies. As shown in Fig. 4, this is particularly problematic when the output common-mode voltage is initially low. In this case, the pull-down paths are turned off as the gates of  $M_{1,2}$ are low. At the same time, the common-mode feedback control voltage rises, which also turns off the pull-up paths, leaving the first stage output in a high-impedance state. Notice that if the outputs are fed back to both the nFET and pFET input transistors  $M_{1,2,3,4}$ , the gain of the positive feedback loop will be doubled, which requires a higher CMFB gain and increases the likelihood for initial DC latch-up. To ensure reliable start-up, we added a pair of diode-connected transistors at the output of the first stage connecting to ground. This scheme provides additional current paths through the diode-connected transistors when both the pull-up and pull-down paths are initially turned off. The resulting leakage currents are negligible during normal operation of the amplifier.

# IV. MEASUREMENT RESULTS OF THE BIOPOTENTIAL AMPLIFIERS

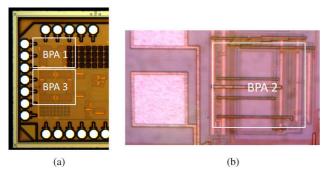

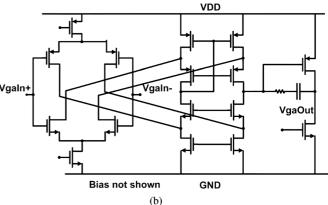

The telescopic-cascode (BPA1) and complementary-input (BPA3) closed-loop biopotential amplifiers were both fabricated in 0.13  $\mu$ m process. We used Metal-Insulator-Metal (MIM) capacitors for their high density, good linearity, and low substrate capacitance. The complementary-input open-loop

Fig. 5. Microphotographs of BPA1, BPA2, and BPA3. (a) BPA1 and BPA3. (b) BPA2.

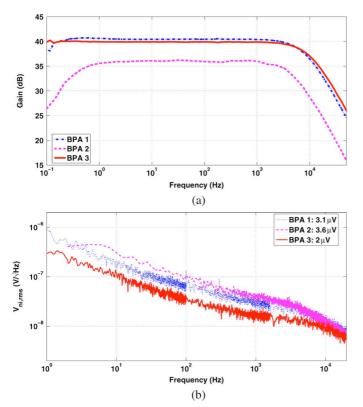

Fig. 6. (a) Gain magnitude response. Bode magnitude comparison of the three BPAs. (b) Input-referred noise. Measured input-referred noise comparison of the three BPAs.

biopotential amplifier (BPA2) was fabricated in 0.5  $\mu$ m SOI-BiCMOS process and employed CMOS devices exclusively. The amplifier occupies 33 000  $\mu$ m<sup>2</sup>. The circuit operates from a supply between 1 V and 5 V. The telescopic-cascode amplifier (BPA1) occupies 46 800  $\mu$ m<sup>2</sup> with 57.8% used for capacitors. The complementary-input closed-loop amplifier (BPA3) occupies 71 750  $\mu$ m<sup>2</sup>, 67.4% of which is occupied by capacitors. A die photo containing BPA1 and BPA3 is shown in Fig. 5(a) and (b). The measurements of all the three amplifiers presented here were taken with a 1 V supply.

Fig. 6(a) compares the measured frequency response of the three BPA designs. The mid-band gains of BPA1 and BPA3 are 40.5 dB and 40 dB, respectively. The different high-pass corner frequencies of BPA1 and BPA3 are due to different lengths of

PMOS transistors used to realize the pseudoresistors. Specifically, four cascaded PMOS transistors of 40  $\mu$ m length are used in BPA3, compared with two cascaded PMOS transistors of  $50 \,\mu \text{m}$  length in BPA1, resulting in higher effective resistance. A larger effective resistance results in a lower high-pass corner at the cost of a higher thermal noise (the larger device sizes in the pseudoresistors result in larger input capacitive divider (1). A comprehensive analysis of pseudoresistor noise contribution is given in [4]. The -3 dB low-pass corners occur at approximately 8 kHz for BPA1, and 10 kHz for BPA3. The difference is attributed to the larger effective transconductance  $G_m$  of BPA3 compared with that of BPA1. The compensation capacitor used in BPA3 is larger than BPA1. The measured mid-band gains of BPA2 are 36 and 44 dB, and the -3 dB low-pass corners are 4.7 kHz and 1.9 kHz for minimum and maximum gain settings, respectively. The gain variation measured across 10 chips was 2 dB. For the remainder of the discussion regarding BPA2, we will primarily focus on the lowest gain setting [shown in Fig. 6(a)] because it provides comparable bandwidth to the other two amplifiers.

Fig. 6(b) compares the measured input-referred noise spectrum of the three BPAs. Consistent with our analysis, the noise of BPA1 is higher than that of BPA3 due to the higher effective  $G_m$  of the first stage of BPA3. The noise spectrum of BPA2 is higher than that of the other amplifiers because of a lower bias current resulting in a higher thermal noise in BPA2. The measured input-referred noise of BPA1, BPA2 and BPA3 integrated from 0.1 Hz to 25 kHz are 3.1  $\mu$ V, 3.5  $\mu$ V and 2  $\mu$ V respectively. Although flicker noise corners are high (800 Hz–1 kHz) in all three cases, the measured flicker noise contributes approximately 20% of the total integrated noise. Flicker noise can be further reduced by employing chopper-stabilization techniques [24], [25]. We have extended our measured noise profile based on a conservative one-pole (20 dB) roll-off to  $10 \times$  the bandwidth of the amplifiers to allow consistent comparison with the literature. The input-referred noise integrated from 0.1 Hz to 105 kHz is respectively 3.2  $\mu$ V, 3.6  $\mu$ V, and 2.2  $\mu$ V.

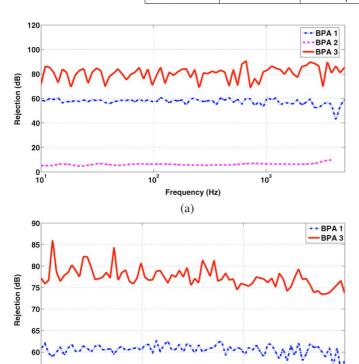

Fig. 7(a) compares the PSRR of the three BPAs. The PSRR for BPA1 is approximately 20 dB lower than that of BPA3. The supply coupling of BPA3 is attenuated by the ratio  $(g_{m6})/((g_{m3}+g_{m4}))\cdot(1-(V_{g6})/(V_{dd}))$  before amplified by the mismatches in  $M_3$  and  $M_4$ , consistent with the analysis in (14). Due to the single-ended nature of BPA2, the positive and negative supplies directly modulate the pFET and nFETs, respectively. Therefore, we expect that the gain from the power supply to the output will be approximately half the gain from input to output. This results in an expected PSRR of 6 dB, consistent with the measured PSRR of 5.5 dB at low frequencies.

Fig. 7(b) compares the CMRR of BPA1 and BPA3. The CMRR for BPA1 has an average value of 60 dB, compared with 80 dB for BPA3. The larger devices in BPA3 should result in smaller expected values of CMRR due to reduced mismatch.

Finally, the linearity of the amplifiers are examined. Many papers use total harmonic distortion (THD) to describe linearity. However, in our experience, the main concern for spike-recording applications is gain compression due to interferers such as electromagnetic interference or low frequency local field potentials that can result in time-varying gain.

55 10

|                  | Specs          | BPA1                | BPA2                 | BPA3                 |  |

|------------------|----------------|---------------------|----------------------|----------------------|--|

| Gain             | ≥ 40 dB        | 40.5 dB             | 36.1 dB              | 40 dB                |  |

| $I_{Amp}$        | minimize       | 12.5 μA             | 805 nA               | 12.1 $\mu$ A         |  |

| NEF              | minimize       | 4.5                 | 1.9                  | 2.9                  |  |

| $v_{ni,RMS}$     | $< 10 \ \mu V$ | $3.2~\mu V$         | 3.6 μV               | 2.2 μV               |  |

| THD(@ input)     | minimize       | 1.5% @ 1 mVpp       | 7.1% @ 1 mVpp        | 1% @ 1 mVpp          |  |

| PSRR             | ≥ 60 dB        | ≥ 60 dB             | 5.5 dB               | ≥ 80 dB              |  |

| CMRR             | ≥ 60 dB        | 60 dB               | _                    | 80 dB                |  |

| Bandwidth        | 0.5 Hz - 7 kHz | .4 Hz - 8.5 kHz     | .3 Hz - 4.7 kHz      | .05 Hz - 10.5 kHz    |  |

| $Z_{in}$ @ 1 kHz | a few MΩ       | 8 MΩ                | 22 MΩ                | $4~\mathrm{M}\Omega$ |  |

| Area             | minimize       | $.047 \text{ mm}^2$ | .046 mm <sup>2</sup> | $.072 \text{ mm}^2$  |  |

| Tech.            | _              | .13 μm              | .5 μm                | .13 μm               |  |

TABLE IV

PERFORMANCE SUMMARY OF THE PRESENTED BIOPOTENTIAL AMPLIFIERS

Fig. 7. (a) PSRR bode magnitude comparison of the three BPAs. (b) CMRR magnitude comparison of BPA1 and BPA3.

Frequency (Hz)

(b)

10

10

Therefore, we posit that it is more useful to characterize the -1 dB gain compression point (approximately 89% of voltage gain) than THD for these amplifiers. This metric also provides a simple "max signal level" specification that facilitates matching amplifiers with various applications. We will thus evaluate the linearity performance by comparing their -1 dB gain compression input voltage. The -1 dB gain compression point occurs at input level of 3 mV for BPA1, 1.8 mV for BPA2, and 4 mV for BPA3. As expected, the open-loop amplifier exhibits more nonlinearity than the closed-loop amplifiers. The difference between the two closed-loop amplifiers BPA1 and BPA3 can be attributed to the complementary-input topology employed in BPA3. Since linearity performance is enhanced through feedback, a high loop gain, or a large open-loop gain given the same feedback ratio is desired. Because the input drives both the nFETs and pFETs, a larger signal swing is allowed at the input before significantly attenuating the open-loop gain and exacerbating the linearity performance.

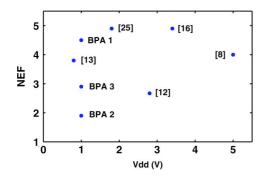

To compare our noise and power performance to other amplifiers, we use the noise efficiency factor (NEF) [1]

$$NEF = V_{rms,in} \sqrt{\frac{2 \cdot I_{total}}{\pi \cdot U_T \cdot 4kT \cdot BW}}.$$

(16)

Where  $I_{\rm total}$  is the total amplifier supply current,  $U_T$  is the thermal voltage kT/q, BW is the amplifier bandwidth, and  $V_{ni,\rm rms}$  is the amplifier's input-referred RMS voltage noise.  $V_{ni,\rm rms}$  used here for the NEF calculation is integrated up to 105 kHz. This FOM normalizes the input-referred rms noise voltage to that of an ideal single-transistor bipolar amplifier with equal current consumption and bandwidth.

The measured performance of BPA1, BPA2, and BPA3 are summarized in Table IV. The open-loop complementary-input amplifier (BPA2) design achieves the best NEF (1.9). However, its poor PSRR performance (5.5 dB) offloads extremely stringent noise and power-supply rejection requirements to the voltage regulation circuitry, potentially increasing the design complexity and power consumption of the system. Although BPA2 has limited application in realistic recording scenarios, it served as a stepping-stone to the design of BPA3. By employing fully-differential closed-loop architecture, BPA3 achieves favorable power-noise tradeoff as well as sufficient PSRR (≥80 dB) and linearity performances (1% THD at 1 mV peak-to-peak input voltage) for practical recording use.

The three amplifiers are compared with a few other state-ofthe-art neural amplifiers in Table V. BPA2 achieves the best NEF (1.9) with a compromise in linearity and PSRR. BPA3 has better NEF performance (2.9) than all the referenced closedloop amplifiers except [12]. However, the low-frequency highpass corner in [12] is three orders of magnitude higher than BPA3, significantly filtering out the 1/f noise. The BPA3's inputreferred noise can be reduced and NEF can be improved by increasing the high-pass corner. In addition to sufficient gain and linearity, BPA3 also achieves comparable PSRR and CMRR performance compared to the other amplifiers despite its low supply voltage, enabling realistic recording scenarios accompanied by power supply noise, electromagnetic (EM) interference and crosstalk. While it is difficult to compare the area due to different technologies used, it is desirable to reduce the size of the amplifiers when scaled up to a multichannel system. Area can be further reduced by stacking metal-insulator-metal (MIM)

|                          | BPA1    | BPA2    | BPA3      | [8]       | [25]    | [12]    | [13]    |

|--------------------------|---------|---------|-----------|-----------|---------|---------|---------|

| Vdd (V)                  | 1       | 1       | 1         | +/-2.5    | 1.8-3.3 | 2.8     | 0.8-1.5 |

| I <sub>Amp</sub> (μA)    | 12.5    | 0.8     | 12.1      | 16        | 1.2     | 2.7     | 0.33    |

| NEF                      | 4.5     | 1.9     | 2.9       | 4.0       | 4.9     | 2.67    | 3.8     |

| NEF 2. Vdd               | 20.3    | 3.6     | 8.4       | 80        | 43.2    | 20      | 11.6    |

| Gain (dB)                | 40.5    | 36      | 40        | 39.5      | 45.5    | 30.8    | 40.2    |

| 1 dB comp.(@ Input) (mV) | 3       | 1.7     | 4         | _         | _       | _       | _       |

| $v_{ni,RMS} (\mu V)$     | 3.2     | 3.6     | 2.2       | 2.2       | 0.93    | 3.06    | 2.7     |

| PSRR (dB)                | ≥ 60    | 5.5     | $\geq 80$ | ≥ 85      | _       | 75      | 62-63   |

| Bandwidth (Hz)           | .4-8.5k | .3-4.7k | .05-10.5k | .025-7.2k | .5-180  | 45-5.3k | 3m-245  |

| Area (mm <sup>2</sup> )  | .047    | .046    | .072      | .16       | _       | .16     | 1       |

| Technology (µm)          | .13     | .5      | .13       | 1.5       | 0.8     | .5      | .35     |

TABLE V

PERFORMANCE COMPARISON OF BIOPOTENTIAL AMPLIFIERS

Fig. 8. Performance comparison of state-of-the-art biopotential amplifiers

Fig. 9. Top-level block diagram of the 500  $\mu$ W neural interface system IC.

capacitors above the amplifier transistors. These modifications would result in a 50% reduction in area.

Although NEF contains current, noise, and bandwidth information, all of which are important, our system-level integration efforts (next section) have revealed that a low (1 V) supply voltage is desirable. This allows integration of complex systems into fine-line (0.13  $\mu$ m and below) CMOS processes that nominally use a 1.2 V supply. These processes allow a) integration of very low power synthesized logic, b) high  $f_T$  allowing low power RFIC design on the same chip, and c) MIM capacitors with high-density and precision that we heavily utilize in our amplifiers. Because the conventional NEF does not consider the supply voltage, a modified metric NEF<sup>2</sup> · Vdd [18] is included in Table V. We can see that BPA3 achieves the best modified NEF compared to other state-of-the-art amplifiers. Fig. 8 also highlights the superior NEF performance of BPA3 compared to other amplifiers operating at similar supply voltages ([13] and [25]), or significantly lower supply voltage for the amplifier with comparable NEF performance ([12]).

#### V. SYSTEM-LEVEL IMPLEMENTATION

We have demonstrated the practical implementation of BPA3 in a neural interface that wirelessly streams a digitized neural

Fig. 10. (a) The closed-loop schematic of the VGA and the Gm cell. (b) VGA double-folded cascode OTA schematic.

waveform over 10 m [23]. As shown in Fig. 9, the neural interface comprises an analog front-end (AFE) with variable gain from 42 to 78 dB, an 8 b successive approximation (SAR) ADC, and a Medical Implant Communication Service (MICS)-band (402 to 405 MHz) FSK transmitter. Continuous spike data is sampled at 8 b, 9.1 kS/s with 3 b of interleaved synchronization packet headers, then transmitted at 100 kb/s. We target the maximum allowable MICS-band EIRP of -16 dBm (25  $\mu$ W) to maximize the wireless communication range.

The low-noise AFE includes the BPA3 presented above AC-coupled to a variable-gain amplifier (VGA) with 6 variable gain and 7 variable high-pass corner settings [Fig. 10(a)]. The VGA consists of a complementary rail-to-rail folded cascode core to improve the input signal swing [Fig. 10(b)]. The closed-loop gain can be adjusted from 0–38 dB by selecting different feedback capacitors. The variable low frequency corners are set from 1 Hz to 300 Hz by programming the feedback transconductor bias current. The feedback transconductors are linearized  $g_m$  cells with bias current as small as a few nAs.

Alternatively, pseudoresistor feedback can be selected to obtain a 1-Hz low-frequency corner. This is helpful in amplifying signals with frequency content below 10 Hz (e.g., LFP, ECoG or electromyography (EMG). The transmitter achieves high power efficiency (16%) by directly modulating the reference oscillator at 44.545 MHz and driving a 9 × frequency multiplying power amplifier. FSK modulation is realized by directly pulling a 4 pF on-chip capacitor, creating a 16.5 kHz  $\Delta f_{\rm ref}$  and 148 kHz  $\Delta f_{\rm rf}$  at 400 MHz. An edge-combiner uses 9 equally-spaced edges generated by a DLL. Operating the entire DLL at  $f_{\rm ref}$  (instead of  $f_{\rm rf}$ ) enables significant power savings while ensuring quartz stability.

This system occupies a die area of  $2.5 \times 1~\text{mm}^2$  using 0.13  $\mu\text{m}$  process. The only off-chip components used in this system are two quartz resonators and 5 passive components used for impedance matching and system clock generation. The system consumes a total of 500  $\mu\text{W}$  with a 30  $\mu\text{W}$  AFE, sub- $\mu\text{W}$  ADC and a 400  $\mu\text{W}$  transmitter. This ultra-low-power sensing platform enables continuous monitoring of electrophysiological activity in untethered animals, providing unprecedented opportunities for neuroscience and medical research.

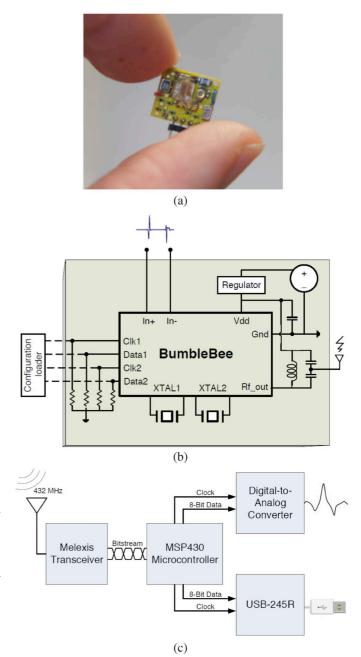

Miniaturization of wireless neural interface systems enables more profound discoveries in neuroscience and clinical research. A reduced board size of  $7.6 \times 8.7 \text{ mm}^2$  was used for deployment, resulting in a system we call the "Bumblebee" [26]. As shown in Fig. 11(a) and (b), This miniaturized board contains a custom IC, all necessary passive components, and a coin-cell battery. The entire system is powered from the single battery, which is subsequently regulated to 1 V. Since there is no non-volatile memory on-chip, an external programmer is required to load appropriate settings for the chip upon powerup. Bumblebee is entrely self-contained and ideal for a variety of sensing/recording applications (EMG, spike-based, audio). We have also developed a low-cost companion receiver for the Bumblebee. The receiver is not power constrained because it can sit at a basestation. Fig. 11(c) shows the block diagram of the receiver. The receiver reads the data wirelessly transmitted from the Bumblebee, performs clock and data recovery, and reconstructs the analog signal. Simultaneously, it sends digital sample data over a standard USB link to a PC for further processing

To power the entire system on a single coin-size battery, traditional sensor network Zigbee-type radios are unsuitable because they consume >20 mW during transmission as well as high average power dissipation. Since the energy density of low mass batteries is extremely limited, sub-mW power dissipation of the IC is mandatory for a reasonable lifespan.

We regularly utilize the Bumblebee to transmit biosignal data to a custom-designed USB-compatible 433 MHz receiver dongle. The chip runs for approximately 3 days continuously on one 0.17 g hearing aid battery.

# VI. IN-VIVO TESTING

We have tested the neural interface system described above in various realistic electrophysiological signal-recording scenarios, including two separate *in-vivo* neural-recording experiments from a rat and a mouse, EMG and electrocardiography (ECG) signal acquisition from humans. All these

Fig. 11. (a) The Bumblebee, a miniaturized, ultra lightweight, low power wireless sensor platform. (b) The functional block diagram of the Bumblebee. (c) The block diagram of the custom receiver.

experiments have successfully verified the system's compatibility with the high source impedance of neural electrodes. Because extreme care has been taken in the experiment setup (e.g., short input wire length, proper grounding, effective input high-pass filtering, etc.), no significant 50/60 Hz line noise was observed throughout the various experiments. BPA3 has proved to be extremely robust in terms of adequate ESD protection, immunity to ambient line noise, RF interference coupled from the on-chip/board supplies and substrate, and reliable start-up.

#### A. Spike-Recording From a Rat

In the first experiment, we recorded from a rat motor cortex using neural electrodes from NeuroNexus Technology. The tungsten electrodes are insulated with teflon, and have an

Fig. 12. BPA3 tested in vivo in rat motor cortex. (a) Recorded rat spike. (b) Two classes of spikes sorted by post-processing programs.

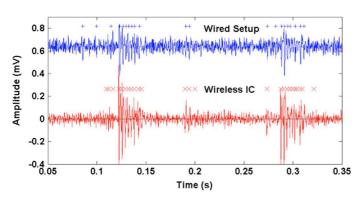

Fig. 13. Neural recording from a mouse visual cortex through two adjacent electrodes. The top is recorded through a rack-mount wired setup, while the bottom reconstructed from the Bumblebee in real time.

equivalent impedance of 100–500 k $\Omega$  measured at 1 kHz [27]. After having identified active spiking cells from traditional rack-mounted instrumentation, we then began recording data directly from the VGA output. By keeping the input wires short and setting the high-pass corner to 200 Hz, no significant low-frequency interference was observed during the experiment. Fig. 12(a) shows a single recorded rat spike. Fig. 12(b) shows sorted spikes recorded through our prototype amplifiers. The two types of spikes line up well, demonstrating extremely high fidelity neural recording achieved from a 1 V supply with less than 28  $\mu$ W power consumption per channel.

# B. Spike-Recording From a Mouse

In the second experiment, the wireless Bumblebee board was used to record from a mouse visual cortex using NeuroNexus A-16 Series probes. The probes were implanted approximately 800  $\mu m$  into the brain. As the stimulus, a white moving bar on the computer monitor was presented to the mouse, simultaneous recordings were conducted through the Bumblebee and a conventional rack-mounted wired setup from two adjacent electrodes. The extra-cellular action potentials were adequately amplified, filtered, digitized and transmitted using the Bumblebee.

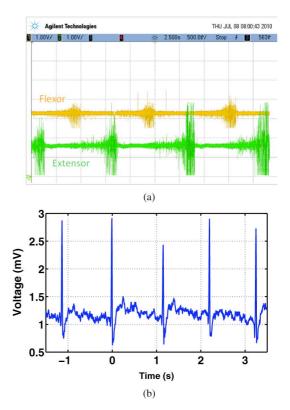

Fig. 14. (a) EMG traces from human flexor and extensor regions simultaneously captured, wirelessly transmitted by two Bumblebee chips, and reconstructed in real-time. (b) Human ECG captured, wirelessly transmitted by a Bumblebee, and reconstructed.

Fig. 13 shows the neural recording from the wired setup (top) and the reconstructed neural signal received from the Bumblebee 3 meters away (bottom). Detected spike occurrences are also marked in the figure. With the two electrodes spaced apart only by 200  $\mu$ m, close resemblance of neural activity can be observed between the two. The detected spikes from the Bumblebee's recording have been used to successfully map the visual receptive field of mouse neurons in the visual cortex.

## C. EMG-Recording From Humans

In addition to recording neural signals, we also verified usability of our prototype Bumblebee in other recording scenarios. For instance, we measured EMG signals from self-adhesive surface electrodes attached to the flexor and extensor muscles of a human arm. Fig. 14(a) shows two EMG traces recorded from a human flexing his arm in quick succession. We have incorporated this miniaturized wireless EMG recording device into a system that provides real-time feedback to subjects for rehabilitation therapy.

#### D. ECG-Recording From Humans

Similarly, We measured ECG signals from self-adhesive surface electrodes attached to a human chest. Fig. 14(b) shows the recorded ECG trace. Thanks to the VGA, we can adjust the AFE gain based on the input amplitude in various recording applications to maximize the signal-to-noise ratio (SNR) without incurring saturation. We have successfully demonstrated the usability of the system for signals with amplitudes as small as tens of  $\mu$ Vs (spikes), and as large as a few mVs (EMG, ECG).

## VII. DISCUSSION

Although this paper intends to focus on the circuit design of low-power BPAs, the analysis should also be considered in the context of a multichannel system. In addition to increased area and power, the larger system also poses additional design constraints on the output impedance of the amplifiers interfacing with the ADC, transmit data rate, input impedance of the amplifiers, and crosstalk. To conserve area and power dedicated to the ADC, DSP, and transmitter circuitry, the outputs of front-end amplifiers are typically multiplexed before digitization.

The circuitry interfacing with the ADC needs to have low enough output impedance such that the sample-and-hold at the ADC input can settle within the acquisition time of the ADC (a few ADC clock periods) to an error smaller than the ADC resolution. We use a VGA between BPA3 and the ADC to enable the recording of a variety of electrophysiological signals. It also decouples the ADC drive requirement from the power consumption of the BPA. Thanks to a more relaxed noise specification, the VGA's current can be concentrated in the second stage, reducing the output impedance. The relationship between the (SAR) ADC acquisition time  $(T_{acq})$  and the VGA output impedance  $(R_{\text{out}})$  can be summarized in (17), where  $N_{\text{acq}}$  and  $N_b$  represent the number of ADC clock cycles dedicated to acquisition and conversion, and  $N_{\rm ch}$ ,  $f_s$ ,  $C_{\rm sample}$  represent the number of channels, sample rate per channel, and the size of the sampling capacitor at the ADC input.

$$T_{\text{acq}} = \frac{N_{\text{acq}}}{N_{\text{ch}} \cdot f_s \cdot (N_{\text{acq}} + N_b)}$$

$$= \ln(2^{N_b}) \cdot R_{\text{out}} \cdot C_{\text{sample}}$$

(17)

For instance, if 16 channels sampling at 10 kSamples/s/channel are muxed before an 8-bit SAR ADC with a 3-cycle acquisition time and a 2 pF input capacitance, the output impedance of the VGA is required to be  $<\!400~\mathrm{k}\Omega.$  In the Bumblebee, for example, a 5  $\mu\mathrm{W}$  VGA was used to provide an output impedance that varies from 700  $\Omega$  to 50 k $\Omega$  as the gain varies from 0 to 38 dB, contributing sufficient drive strength. As discussed later, channel crosstalk also requires low output impedance of the amplifiers muxed prior to the ADC.

The input impedance of the front-end BPAs is mostly capacitive, and should be significantly higher than the impedance of the electrodes to minimize the input signal attenuation from the capacitive divider formed at the electrode-tissue interface. This is especially important in a multichannel system, where one signal electrode is used per channel while one reference electrode is shared among all the channels. The size of the reference electrode is usually a few orders of magnitude larger than the signal electrode. As a result, a common interference signal (e.g., EM or power supply noise) presented to a signal electrode and the reference electrode is converted to differential signals at the BPA inputs as it experiences different amount of attenuation from the capacitive dividers [28]. When a closed-loop amplifier with capacitive feedback is used (e.g., BPA1 and BPA3), the input capacitance  $(C_i)$  within the signal bandwidth approximately equals the input DC-blocking capacitors  $(C_s)$ . While the potential divider effect at the electrode-chip interface discussed above sets the upper bound for  $C_s$ , the capacitive divider at the OTA input sets the lower bound for  $C_s$  to minimize the

increase in the input-referred noise (1). The  $C_i$  in BPA1, BPA2 and BPA3 provides impedances of  $\approx 8 \text{ M}\Omega$ , 22 M $\Omega$  and 4 M $\Omega$  at 1 kHz respectively, high enough to interface with electrodes, while ensuring a sufficiently low input-referred noise.

Crosstalk is also an issue in a multichannel system. First, there is crosstalk from the capacitive coupling between electrode probes. As feature sizes reduce, the electrical crosstalk due to electrical coupling also increases [3]. In our in-vivo experiments, we used tungsten electrodes with 200  $\mu$ m spacing on a silicon substrate, which resulted in an approximately <1 pF coupling capacitance  $(C_c)$ . The impedance magnitude of the electrode  $(C_e)$  is roughly 0.5 M $\Omega$  at 1 kHz. Although we cannot measure crosstalk with our single-channel prototype, we can approximate the first-order crosstalk from the capacitive divider  $C_c/(C_c + C_e + C_i)$  to be 0.3%, or -50 dB, where  $C_c =$  $1~{\rm pF},\,C_e\,=\,318~{\rm pF},\,C_i\,=\,40~{\rm pF}.$  Secondly, there is crosstalk due to substrate (or supply) coupling. In the audio frequency range of interest here, these sources of coupling can be minimized through careful layout. Sufficient PSRR also ensures adequate rejection of the noise coupled in the supply. Additionally, there is crosstalk in the circuit block that muxes all the channels into the ADC. The off resistance of the switches forms a resistive divider with the input impedance of the ADC in parallel with the impedance of the other channels, leading to signal crosstalk. High off resistance of the switches and low output impedance of the muxed amplifiers are required to minimize the signal crosstalk. For our VGA/MUX/ADC, simulations reveal a crosstalk of < -80 dB, reducing the input-referred mux crosstalk to below the noise floor.

#### VIII. CONCLUSION

Reducing the power consumption of BPAs while ensuring sufficiently low noise is essential in reducing the power consumption of a biopotential-recording system. In this paper, we discussed the progression of three BPA designs: a closed-loop fully-differential telescopic-cascode amplifier (BPA1), an open-loop complementary-input (BPA2), and a closed-loop fully-differential complementary-input amplifier (BPA3) that leverages the salient design techniques of the first two amplifiers. The three BPAs exhibit low input-referred integrated noise of 3.2  $\mu$ V, 3.6  $\mu$ V and 2.2  $\mu$ V while consuming 12  $\mu$ W,  $0.8 \mu W$ , and  $12 \mu W$  respectively under 1 V supply. Consistent with theory, BPA1 using conventional architecture has an NEF comparable to the prior work. BPA2 and BPA3 achieve significantly better power-noise performance than BPA1 due to the power-efficient complementary-input topology. While the practical use of BPA2 is still an active area of research, BPA3 not only achieves superior power-noise tradeoff under low power supply conditions, but also ensures robust performance in realistic recording scenarios. We have demonstrated the robustness of BPA3 in a low power wireless system on chip that has been deployed in many *in-vivo* experiments. The scalability of the amplifier is also analyzed in the context of multichannel biopotential-recording applications.

#### ACKNOWLEDGMENT

The authors gratefully acknowledge Prof. C. Moritz (University of Washington Rehab Medicine) and Prof. E. Fetz (University of Washington Physiology and Biophysics), as well as

H. Zariwala and T. Nghi Nguyen from the Allen Institute for Brain Science for their *in-vivo* experiment assistance.

## REFERENCES

- M. Steyaert and W. Sansen, "A micropower low-noise monolithic instrumentation amplifier for medical purposes," *IEEE J. Solid-State Circuits*, vol. 22, pp. 1163–1168, 1987.

- [2] C. Nordhausen, E. Maynard, and R. Normann, "Single unit recording capabilities of a 100-microelectrode array," *Brain Res.*, vol. 726, pp. 129–140, 1996.

- [3] K. Najafi and K. Wise, "An implantable multielectrode array with on-chip signal processing," *IEEE J. Solid-State Circuits*, vol. 21, pp. 1035–1044, 1986.

- [4] R. Harrison, "The design of integrated circuits to observe brain activity," *Proc. IEEE*, vol. 96, pp. 1203–1216, Mar. 2008.

- [5] A. B. Schwartz, X. T. Cui, D. J. Weber, and D. W. Moran, "Brain controlled interfaces: Movement restoration with neural prosthetics," *Neuron*, vol. 52, pp. 205–220, 2006.

- [6] E. Kandel, J. Schwartz, and T. Jessell, Principles of Neural Science. New York: McGraw-Hill, 2000.

- [7] E. Leuthardt, G. Schalk, J. Wolpaw, J. Ojemann, and D. Moran, "A brain-computer interface using electrocorticographic signals in humans," *J. Neural Eng.*, vol. 1, no. 2, pp. 63–71, 2004.

- [8] R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," *IEEE J. Solid-State Circuits*, vol. 38, pp. 958–965, 2003.

- [9] T. Jochum, T. Denison, and P. Wolf, "Integrated circuit amplifiers for multi-electrode intracortical recording," *J. Neural Eng.*, vol. 6, no. 1, p. 012001, 2009.

- [10] A. Chandran, K. Najafi, and K. Wise, "A new DC baseline stabilization scheme for neural recording microprobes," in *Proc. 1st Joint BMES/EMBS Conf.*, Atlanta, GA, 1999.

- [11] I. Olsson, R. H., M. Gulari, and K. Wise, "Silicon neural recording arrays with on-chip electronics for in-vivo data acquisition," in *Proc.* 2nd Annu. Int. IEEE-EMB Special Topic Conf. Microtechnologies in Medicine and Biology, 2002.

- [12] W. Wattanapanitch, M. Fee, and R. Sarpeshkar, "An energy-efficient micropower neural recording amplifier," *IEEE Trans. Biomed. Circuits Syst.*, vol. 1, no. 2, pp. 136–147, 2007.

- [13] H. Wu and Y. P. Xu, "A 1 V 2.3  $\mu$ W biomedical signal acquisition IC," in *Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, Jun.–Sep. 2006, pp. 119–128.

- [14] M. S. Chae, Z. Yang, M. Yuce, L. Hoang, and W. Liu, "A 128-channel 6 mW wireless neural recording IC with spike feature extraction and UWB transmitter," *IEEE Trans. Neural Syst. Rehabil. Eng.*, vol. 17, no. 4, pp. 312–321, Aug. 2009.

- [15] A. Nurmikko, J. Donoghue, L. Hochberg, W. Patterson, C. Y.-K. S. Bull, D. Borton, F. Laiwalla, and J. S. P. Y. M. Aceros, "Listening to brain microcircuits for interfacing with external world-progress in wireless implantable microelectronic neuroengineering devices," *Proc. IEEE*, vol. 98, pp. 375–388, 2010.

- [16] M. Yin and M. Ghovanloo, "A low-noise preamplifier with adjustable gain and bandwidth for biopotential recording applications," in *Proc.* IEEE Int. Symp. Circuits and Systems, 2007.

- [17] M. Mollazadeh, K. Murari, G. Cauwenberghs, and N. Thakor, "Micropower CMOS integrated low-noise amplification, filtering, and digitization of multimodal neuropotentials," *IEEE Trans. Biomed. Circuits Syst.*, vol. 3, no. 1, pp. 1–10, Feb. 2009.

- [18] R. Muller, S. Gambini, and J. Rabaey, "A 0.013 mm<sup>2</sup> 5 μW dc-coupled neural signal acquisition IC with 0.5 V supply," in *Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, Feb. 2011, pp. 302–304.

- [19] B. Gosselin, A. Ayoub, J.-F. Roy, M. Sawan, F. Lepore, A. Chaudhuri, and D. Guitton, "A mixed-signal multichip neural recording interface with bandwidth reduction," *IEEE Trans. Biomed. Circuits Syst.*, vol. 3, no. 3, pp. 129–141, Jun. 2009.

- [20] C. Enz, F. Krummenacher, and E. Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications," *Analog Integr. Circuits Signal Process.*, vol. 8, pp. 83–114, Jul. 1995.

- [21] B. Razavi, Design of Analog CMOS Integrated Circuits. Noida, India: Tata McGraw-Hill, 2000.

- [22] J. Holleman and B. Otis, "A sub-microwatt low-noise amplifier for neural recording," in Proc. 29th Annu. Int. Conf. IEEE Engineering in Medicine and Biology Society, 2007.

- [23] S. Rai, J. Holleman, J. Pandey, F. Zhang, and B. Otis, "A 500  $\mu$ W neural tag with 2  $\mu$ V<sub>rms</sub> AFE and frequency-multiplying MICS/ISM FSK transmitter," in *Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, Aug.–Dec. 2009, pp. 212–213, 213a.

- [24] D. Yeager, F. Zhang, A. Zarrasvand, N. George, T. Daniel, and B. Otis, "A 9 μA, addressable Gen2 sensor tag for biosignal acquisition," *IEEE J. Solid-State Circuits*, vol. 45, no. 10, pp. 2198–2209, 2010.

- [25] T. Denison, K. Consoer, W. Santa, G. Molnar, and K. Mieser, "A 2 µW, 95 nV/rtHz, chopper-stabilized instrumentation amplifier for chronic measurement of bio-potentials," in *Proc. IEEE Instrumentation and Measurement Technology Conf.*, Jan.—Mar. 2007, pp. 1–6.

- [26] T. Morrison, F. Zhang, S. Rai, J. Pandey, J. Holleman, and B. Otis, "The bumblebee: A 0.3 gram, 560 μW, 0.1 cm<sup>3</sup> wireless biosignal interface with 10-m range," in *Proc. IEEE Solid-State Circuits Conf., Student Design Contest Winner*, 2010.

- [27] D. Kipke, W. Shain, G. Buzsaki, E. Fetz, J. Menderson, J. Hetke, and G. Schalk, "Advanced neurotechnologies for chronic neural interfaces: New horizons and clinical opportunities," *J. Neurosci.*, pp. 655–660, Oct. 2008.

- [28] E. Spinelli, M. Mayosky, and R. Pallas-Areny, "A practical approach to electrode-skin impedance unbalance measurement," *IEEE Trans. Biomed. Eng.*, vol. 53, no. 7, pp. 1451–1453, 2006.

Fan Zhang (S'08) received the B.S. degree in electrical engineering and computer sciences from the University of California, Berkeley, and the M.S. degree in electrical engineering from the University of Washington, Seattle, in 2007 and 2009, respectively.

Currently, she is working toward the Ph.D. degree at the University of Washington. From 2006 to 2007, she interned at Agilent Technologies, Santa Clara, CA. In 2009, she interned at Intel Corporations, Hillsboro, OR, and worked on modeling

of sigma-delta phase-locked loops. She has worked on low-noise ananlog front-end and system-level designs for biomedical sensing applications. Her current research interests include low-power/low-voltage RF circuit design for biomedical applications.

**Jeremy Holleman** (S'02–M'09) received the B.S. degree in electrical engineering from the Georgia Institute of Technology, Atlanta, in 1997 and the M.S. and Ph.D. degrees in electrical engineering from the University of Washington, Seattle, in 2006 and 2009, respectively.

Currently, he is an Assistant Professor in the Department of Electrical Engineering and Computer Science, University of Tennessee, Knoxville. He has previously worked for Data I/O and National Semiconductor. His research focuses on low-power

integrated circuits for biomedical devices and other wireless sensing applications.

**Brian P. Otis** (S'96–M'05–SM'10) received the B.S. degree in electrical engineering from the University of Washington, Seattle, and the M.S. and Ph.D. degrees in electrical engineering from the University of California, Berkeley.

He joined the faculty of the University of Washington as Assistant Professor of Electrical Engineering in 2005. His primary research interests are ultra-low power RFIC design, FBAR-based clocks, and bioelectrical interface circuits and systems. He previously held positions at Intel Corporation and

Agilent Technologies.

Dr. Otis has served as an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMSIII: EXPRESS BRIEFS. Dr. Otis received the University of California, Berkeley, Seven Rosen Funds Award for innovation in 2003. He was corecipient of the 2002 ISSCC Jack Raper Award for Outstanding Technology Directions Paper, received the National Science Foundation Career Award in 2009, and was awarded the University of Washington College of Engineering Junior Faculty Innovator Award in 2011.